کد VHDL و فایل word پایان نامه طراحی و پیاده سازی یک ریزپردازنده قابل پیکربندی مجدد

- سه شنبه, ۱۱ مهر ۱۳۹۶، ۰۵:۴۵ ب.ظ

- ۰ نظر

فهرست مطالب

چکیده 1 فصل اول:تاریخچه محاسبات با قابلیت پیکربندی مجدد 1-1- مقدمه 3 فصل دوم: مفهوم، معماریها و روشهای طراحی سیستمهای قابل پیکربندی مجدد 2-1- محاسبات و سخت افزار با قابلیت پیکربندی مجدد 8 2-2- پیکربندی مجدد جزئی پویا و ایستا در FPGA ها 10 2-3- معرفی مرجع اول در پیکر بندی مجدد FPGA 11 2-4- معرفی مرجع دوم در پیکر بندی مجدد FPGA 12 2-5- معرفی مرجع سوم در پیکر بندی مجدد FPGA 14 2-6- معرفی مرجع چهارم در پیکر بندی مجدد FPGA 14 2-7- معرفی مرجع پنجم در پیکر بندی مجدد FPGA 15 فصل سوم: پیاده سازی نرم افزاری و سخت افزاری پیکربندی مجدد پیشنهادی 3-1- مقدمه 19 3-2- پیاده سازی جمع کننده CARRY_LOOK_AHEAD به صورت N بیتی 20 3-3- پیاده سازی ضرب کننده به صورت N بیتی 24 3-3-1 ضرب کننده برای دو عدد قدر مطلق علامت 24 3-3-2 ضرب دو عددمتمم 2 یا 2’S 25 3-4- پیاده سازی تقسیم کننده به صورت N بیتی 26 3-5- طراحی سخت افزار و ALU برای پیاده سازی کدها با قابلیت پیکر بندی مجدد 28 3-5-1 طراحی واحد کنترل 28 3-5-2 به کارگیری کنترل های FPGA در طراحی سخت افزاری با سرعت بالا 31

فصل چهارم: نتایج شیبه سازی 4-1- نتایج شیبه سازی در نرم افزار MODELSIM 37 4-2- نتایج شیبه سازی در نرم افزار ISE 39 4-3- مقایسه با مراجع 51 فصل پنجم: نتیجه گیری 5-1- نتیجه گیری 54 فصل ششم: کارهای آینده 6-1- کارهای آینده 56 منابع و مآخذ 57 فهرست منابع انگلیسی 57 پیوست: کدهای نوشته شده VHDL 59 چکیده انگلیسی 68

فهرست جداول

عنوان شماره صفحه جدول 1-1. روند کلی تکامل سیستمهای قابل پیکربندی مجدد 6 جدول 3-1. 4 حالت ممکن برای جمع کننده ADDER_CARRY_LOOK_AHEAD 21فهرست شکل ها

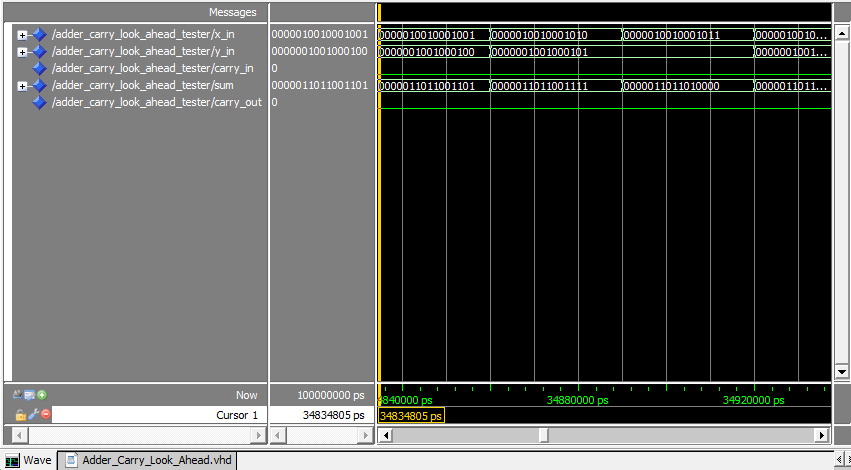

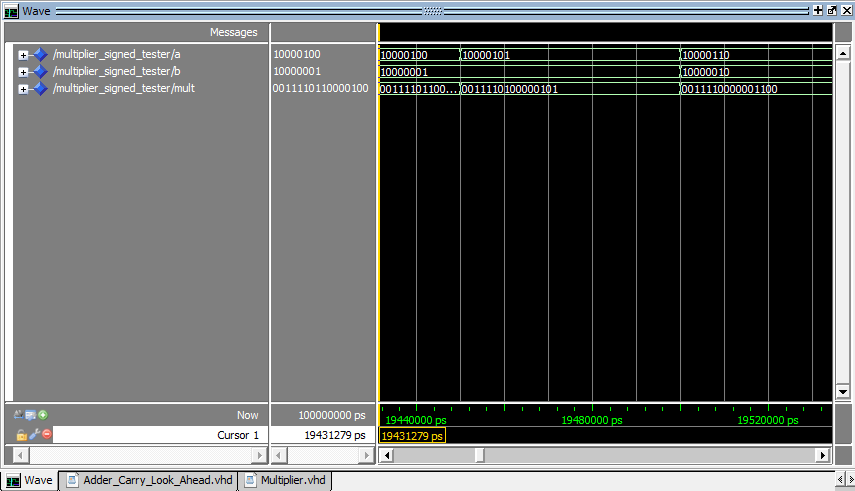

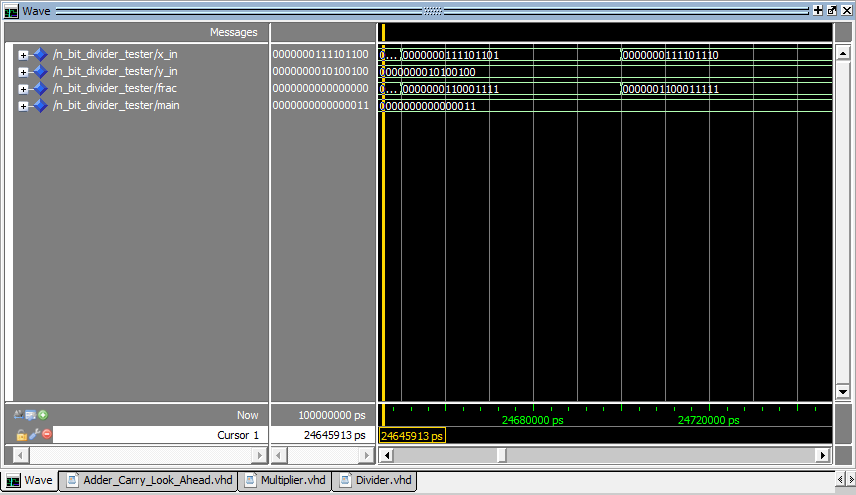

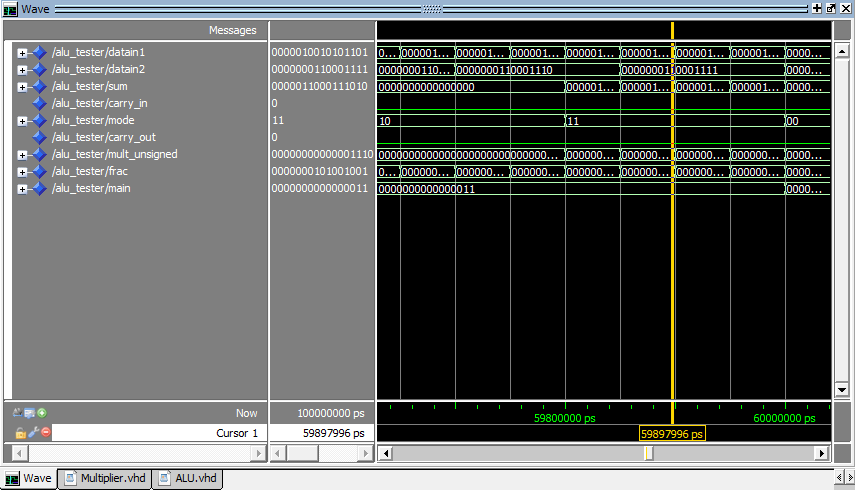

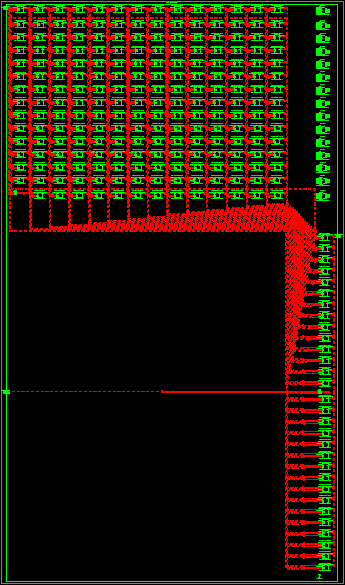

عنوان شماره صفحه شکل 2-1. پیکر بندی مجدد جزئی پویا 10 شکل 2-2. پیکر بندی دوباره جزئی ایستا 11 شکل 2-3. سیستم پیشنهادی مرجع 1 در پیکر بندی مجدد FPGA 11 شکل 2-4. فلو چارت مربوط به مرجع ا 12 شکل 2-5. طراحی در سطح RTL در برد FPGA 13 شکل 2-6. نمونه هایی از پیاده سازی در نرم افزار MODELSIM 13 شکل 2-7. جریان طراحی سنتی برای مفهوم سیستم پیکر بندی مجدد به صورت پویا 14 شکل 2-8. الگوریتم پیکر بندی مجدد جزئی پویا مرجع 4 15 شکل 2-9. بلوک DCM 16 شکل 2-10. طراحی در سطح RTL بلوک DCM 16 شکل 2-11. طراحی سلسله مراتبی مرجع پنجم 17 شکل 2-12. نتایج شبیه سازی DRP بلوک های منطقی 17 شکل 3-1. جمع کننده کامل یا FULL ADDER 21 شکل 3-2. شکل مداری الگوریتم جمع کننده ADDER_CARRY_LOOK_AHEAD 23 شکل 3-3. مدار ضرب کننده برای ضرب دو عدد قدر مطلق علامت 24 شکل 3-4. مراحل ضرب دو عدد 3- و 4- را بیتی به روش قدر مطلق علامت 25 شکل 3-5. عمل تقسیم به روش مقایسه ای 26 شکل 3-6. مثالی از مراحل تقسیم 27 شکل 3-7. واحد کنترل 28 شکل 3-8. نشان دهنده مفهوم روش ریزبرنامه سازی 29 شکل 3-9. فعال شدن هر دستور بر اساس ورودی متناظر در روش سیم بندی شده 30 شکل 3-10. فعال شدن هر دستور بر اساس ورودی متناظر در روش ریز برنامه سازی 30 شکل 3-11. دیاگرام یک بلوک عمومی برای یک سیستم کامل کنترل سرعت بالا 31 شکل 3-12. نمودار بلوکی واحد پردازشی کنترلر طراحی شده بر مبنای FPGA 33 شکل 3-13. نحوه پیاده سازی طرح پیشنهادی در FPGA 34 شکل 4-1. شبیه سازی جمع کننده در نرم افزار MODELSIM 37 شکل 4-2. شبیه سازی ضرب کننده در نرم افزار MODELSIM 38 شکل 4-3. شبیه سازی تقسیم کننده در نرم افزار MODELSIM 38 شکل 4-4. شبیه سازی ALU در نرم افزار MODELSIM 39 شکل 4-5. بلوگ دیاگرام یا شماتیک RTL جمع کننده 41 شکل 4-6. مدار داخلی یا پیکر بندی داخلی مربوط به جمع کننده 41 شکل 4-7. بلوگ دیاگرام یا شماتیک RTL ضرب کننده 43 شکل 4-8. مدار داخلی یا پیکر بندی داخلی مربوط به ضرب کننده 44 شکل 4-9. مدار داخلی یا پیکر بندی داخلی مربوط به ضرب کننده 47 شکل 4-10. بلوگ دیاگرام یا شماتیک RTL تقسیم کننده 48 شکل 4-11. بلوگ دیاگرام یا شماتیک RTL مربوط به ALU 50 شکل 4-12. نمای کلی مدار داخلی یا پیکر بندی داخلی مربوط به ALU 50 شکل 4-13. مدار داخلی یا پیکر بندی داخلی مربوط به ALU 51 شکل 4-14. فلوچارت سیستم پیشنهادی 52چکیده

دو روش کلی در محاسبات برای اجرای الگوریتم¬های مختلف وجود دارد. روش اول، استفاده از ASIC ها میباشد تا بتوانیم الگوریتم مورد نظر را در سختافزار اجرا و پیادهسازی کنیم. چون این تجهیزات برای هر الگوریتم خاص ساخته میشوند، سریع و کارا میباشند. اما مدارات آنها پس از ساخته شدن، تغییر نمیکنند. راه دوم، استفاده از ریزپردازندهها است که بسیار انعطاف پذیرتر می¬باشند. آنها مجموعهای از دستورات را اجرا میکنند و کارایی سیستم را بدون تغییر سختافزار، تغییر می¬دهند. اما، همانند یک ASIC به این دلیل که برای یک کاربرد خاص طراحی نشده¬اند، دارای قابلیت انعطاف نمیباشد. سیستم¬های با قابلیت پیکربندی مجدد به گونه¬ای توسعه یافته است تا فاصله میان سختافزار و نرمافزار را کم کند و همچنین، به یک کارایی بسیار بالاتر از نرمافزار و قابلیت انعطاف بیشتر سختافزار برسد. به همین منظور، در این پایان نامه ابتدا تاریخچهای مختصر از توسعه سیستم¬های با قابلیت پیکربندی مجدد بیان شده است. پس از آن، مفهوم قابلیت پیکربندی مجدد و انواع طراحی آن ارائه شده است. روند طراحی سیستم با قابلیت پیکربندی مجدد بر روی تراشه FPGA آورده شده است. ویژگیهای طراحی سیستم با یک زبان برنامه نویسی بر مبنای VHDL بیان شده است. در نهایت سیستمی به صورت سخت افزاری و نرم افزاری ارائه شده است که قابلیت پیکر بندی مجدد را دارد و با استفاده از پردازش موازی سرعت پیکر بندی مجدد سیستم را افزایش می¬دهد. در ضمن، ایده کار به این صورت است که باس¬های حجیم از سیستم حذف شده و جای خود را به بلوک¬های منطقی دهد. در نهایت، تمامی قسمت¬های پویا و ایستا با هم به طور موازی کار می¬کنند که باعث افزایش سرعت مدار می¬شود.

کلمات کلیدی: پیاده سازی، پیکربندی مجدد جزئی پویا، پیکربندی مجدد جزئی ایستافصل اول: تاریخچه محاسبات با قابلیت پیکربندی مجدد

1-1- مقدمه

مفهوم محاسبات با قابلیت پیکربندی مجدد از اوایل دهه 60 میلادی پدیدار شد. موقعی که مقاله جرالد استرین مفهوم یک کامپیوتر ساخته شده از یک پردازنده استاندارد و آرایه¬ای از سخت افزار قابل پیکربندی مجدد را پیشنهاد کرد. پردازنده اصلی، عملکرد سخت افزار قابل پیکربندی مجدد را کنترل می کند. در نتیجه، این سخت افزار با قابلیت پیکربندی مجدد، برای انجام هر کاری مناسب خواهد بود. برای مثال می¬توان کارهایی نظیر پردازش تصویر، الگوریتم عصبی و تطبیق الگو را با سرعت بالایی انجام داد. به محض اتمام یک کار، سخت افزار می¬تواند برای انجام کار جدید پیکربندی مجدد شود. چنین خاصیتی با ترکیب انعطاف پذیری یک نرم افزار و سرعت یک سخت افزار، در یک ساختار ترکیبی امکان پذیر شده است. در ضمن، چنین ایده¬ای در زمان پیدایش، بسیار جلوتر از تکنولوژی ساخت سخت افزار مورد نیازش بود. در دهه اخیر، تحقیقات زیادی درباره معماری¬های با قابلیت پیکربندی مجدد بوجود آمده است. این معماری¬ها هم در دانشگاه¬ها و هم در صنعت توسعه یافته¬اند. این معماری¬ها در دسته¬های زیر قرار می¬گیرند: • Matrix • Gorp • Elixent • XPP • Silicon Hive • Montium • Pleiades Morphosys • PiCOGA علت عملی بودن چنین طرحهایی، پیشرفت مداوم فنآوری سیلیکونی بوده که پیاده سازی طرح¬های پیچیده را روی یک تراشه امکان پذیر ساخته است. اولین مدل تجاری کامپیوتر با قابلیت پیکربندی مجدد در جهان به نام Algotronix CHS 2*4 در سال 1991 ارائه شد. این طرح به هیچ عنوان موفقیت تجاری نداشت، اما آنقدر امیدبخش بود که شرکت Xilinx (مخترع FPGA) تکنولوژی را خرید و محققان Algotronix را به خدمت گرفت. هم اکنون تعدادی شرکت فروشنده کامپیوترهای با قابلیت پیکربندی مجدد وجود دارند که بازار کامپیوترهای با کارایی بالا را در بر گرفته¬اند. مهمترین این شرکت¬هاSRC Computers ، SGL و Cray می¬باشند. شرکت ابر رایانه¬ای Cray بستر محاسبات قابل پیکربندی مجدد SRC را به دست آورد و آن را به عنوان XD1 به فروش می¬رساند. SGI رایانه RASC را همراه با سری ابر رایانه¬های Altix به فروش می¬رساند. شرکتSRC Computers یک خانواده از رایانه¬های قابل پیکربندی مجدد را توسعه داده است. این خانواده بر اساس معماری ضمنی و پردازنده MAP می¬باشد. تمام آنچه که گفته شد رایانه¬های هیبریدی هستند، که این رایانه¬ها با ریزپردازنده¬های FPGA همراه شده¬اند و با آن ساخته می¬شوند. FPGA ها توسط کاربر برنامه¬ریزی می¬شوند. این سیستم¬ها می¬توانند به عنوان ابر رایانه¬هایی با سرعت بالا با استفاده از FPGA ها به کاربرده شوند. (در حقیقت FPGA ها گزینه ای در XD1 و SGIRASC هستند). پیکربندی XD1 و SGIFPGA از طریق زبانهای توصیف سخت افزار (HDL) صورت می¬گیرد. با به کارگیری زبانهای سطح بالایی نظیر ابزار گرافیکی Star Bridge Viva یا زبانهایی مانند C مثل Handel-C از Celoxica و Lmpulse-C از Impulse Accelerated technologies یاMitrpn-C از Mitrionics و همچنین VHDL و Verilog نیز می¬توان پیکربندی را انجام داد. توسعه کد نویسی منطقی یک FPGA خام، یک فرآیند پیچیده است که نیازمند دانش و ابزار تخصصی است. SRC کامپایلری را ساخته است که زبان سطح بالایی مثل C یا Fortran را به عنوان ورودی می¬گیرد و با تغییراتی اندک، آنها را برای اجرا و پیاده¬سازی روی FPGA در ریزپردازنده، کامپایل می¬کند. بعضی از الگوریتم¬های کاربردی با زبانهای سطح بالا همانند C و Fortran نوشته می¬شوند. کامپایلر (Carte)، حداکثر موازی سازی را در کد انجام می¬دهد و منطق سخت افزار خط لوله¬ای را تولید می¬کند که در MAP ها مقداردهی شده¬اند. همچنین این کامپایلر تمام کدهای واسطی که برای مدیریت انتقال داده در داخل و خارج MAP نیاز است را تولید می¬کنند. این کدهای واسط، وظیفه هماهنگ سازی ریزپردازنده با منطق در حال اجرا در MAP را دارند.

خروجی ها :

- ۹۶/۰۷/۱۱